赤色飓风开发板配套的字符液晶模块为2行,每行16个字符。本实要求显现功用如下:榜首行显现“WelcomeRedLogicWorld!”,第二行显现“RedLogicWorld!”,由于一行只能显现16个字符,因而要整屏左移显现。

本规划的程序首要包括两个模块,一个模块为char_ram,另一个模块为LCD的驱动模块lcd。

char_ram模块的基本功用是根据输入的地址,输出相应字符在CGRM(字符存储发生器)中的地址。由于在操控LCD显现时,只需用户更好的供给相应字符的地址,就能够显现出该字符。

在char_ram中,先设置好一切字符对应的地址,然后给要使用到的字符界说新的地址用于挑选输出。

Lcd模块用于驱动lCD正常作业。LCD是一个慢显现器材,因而时钟一定要满意规则的要求,在这里经过50MHz分频得到输入的时钟周期约为100s(约10Hz),以满意慢显要求。LCD的驱动模块使用一个状态机来完结。具体程序参阅实例源代码。

用户也能够直接新建一个仿真文件,挑选“NewSource”,挑选“VerilogTestFixture”,输入测验文件名称,如图10.38所示,单击“Next”按钮。

挑选lcd模块(对哪个模块来测验,就挑选哪个文件),如图10.39所示。

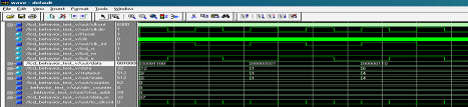

上面列出的许多信号是人为增加的,具体怎么增加以及具体Wave窗口下的许多用法在这里不做具体叙说。需求特别阐明的是,若用户自己装的是ModelSimXE版别,是没办法完结这个仿真的,由于这个工程代码是用VHDL写的,测验代码是用Verilog写的,ModelSimXE版别是不支撑混仿真的,主张装置ModelSimSE版别,SE下是支撑混合仿真的。

这两个波形分别为写数据和写指令的仿真成果。写数据即向DDRAM写入要显现的字符对应的地址,其间clk为体系的输入时钟50MHz,clk_int为分频后得到的约10Hz输入时钟,lcd_e为使能信号,写数据时RS=1,R/W=0,写指令时RS=0,R/W=0。

本节对使用FPGA来驱动字符型液晶模块的办法做了介绍,并经过编译下载在赤色飓风的开发板上完结了预订功用。

上一篇:1602字符型液晶显现篇